AMD Radeon HD 7970显卡深度评测

历史总是惊人地相似,AMD在推出首款DirectX 11显卡以后,再次领先NVIDIA推出首款DirectX 11.1显卡—Radeon HD 7970。这款产品对AMD来说具有划时代的意义,因为它和之前HD 2000~HD 6000系列的任何一款显卡都不同,采用了革命性的GCN图形架构,给出了未来AMD显卡的发展方向。再加上它是第一款采用28nm工艺和支持PCI-E 3.0的显卡,这使得它想不火都难。

架构演变:HD 7970的革命之路

从HD 2000系列开始,一直到HD 5000系列,AMD(ATI)显卡在架构上一直没有本质性的改变,始终采用的是VLIW5设计。新产品只是在上一代产品上小幅修改,并没有实质性的突破。到了Cayman核心的HD 6900系列,AMD意识到既有的架构在DirectX 11游戏和不少应用中出现了瓶颈,一味堆砌核心规格并不能显著提升显卡的性能。于是我们看到,HD 6900系列首次作出了尝试。它将VLIW 5改进到VLIW 4,去掉了一个较大的ALU.trans单元,实现了四个对等的流处理单元,计算效率得到了提升。这样的设计,曾被我们称之为“自R600以来大的架构变革”。不过就在我们以为AMD将会遵循Cayman的“VLIW 4改革步伐”,对下一代产品进行改良和突破时,AMD却悄然推出了采用GCN(Graphics Core Next)全新架构、代号为Tahiti核心设计的HD 7900系列显卡,实现了华丽的转身。

从今天来看,AMD推出Cayman更像是一次在改革路上的投石问路之举,真正的革命则是在Tahiti上。Tahiti的革命之处在于将AMD长久以来坚持的VLIW架构彻底抛弃,为AMD打开了迈向未来通用计算的大门。从目前的计算趋势来看,通用计算在游戏中被大量使用后,将成为显卡性能的约束性因素。对通用计算支持不好的显卡,在遇到需要进行通用计算处理的任务时,如多光源等较复杂的计算时性能会明显下降。目前DirectX 11游戏越来越多,需要应用到通用计算的场合也越来越多,因此AMD选择在这个时候彻底改革架构是相当明智的。另一方面,GPU计算蓬勃发展的时代已经来临,GPU将在高性能计算领域发挥更重要的作用。而AMD过去的VLIW 5、VLIW 4架构的产品在这方面的表现并不好,远远不如NVIDIA。因此AMD欲搭上GPU计算这班高速列车的话,就势必对图形架构进行大刀阔斧的变革。

GCN图形架构解读

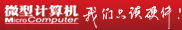

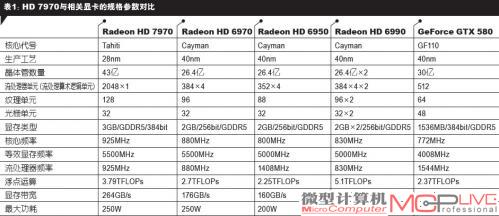

目前,采用Tahiti核心的主要有HD 7970和HD 7950。AMD首先发布的是HD 7970,定位于AMD单核心显卡中的旗舰产品,将接替之前的Radeon HD 6970。它在国内的官方定价为4299元,内建2048个流处理算术逻辑单元、32个CU阵列、128个纹理单元以及32个ROP(光栅处理单元),大浮点计算能力达到了3.79TFLOPs。该卡搭载3GB/GDDR5/384bit显存,核心频率和显存频率分别为925MHz和5500MHz。根据AMD给出的数据,HD 7970在PowerTune大满载功耗下是250W,一般游戏满载功耗是210W,低功耗只有3W,需要8pin+6pin的外接供电。

HD 7950作为采用Tahiti核心的另一款产品,并没有随HD 7970一起发布。目前的消息是,AMD将在1月底或者2月初发布HD 7950。其流处理算数逻辑单元从2048个缩减到1792个,也就是屏蔽了4个CU单元。不过好在它的显存位宽依旧维持在384bit,显存容量保持在3GB不变(下游厂商也可以缩减到1.5GB)。接下来,就让我们从图形架构层面来看看Tahiti的革命性变化吧。

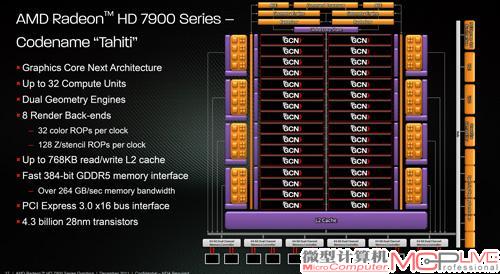

CU单元:基于SIMD阵列的MIMD架构

AMD称GCN在架构设计上为“基于SIMD阵列的MIMD架构(GCN is a MIMD architecture with a SIMD array)”。从AMD的官方表态上我们可以看出,GCN本身并没有彻底地转向MIMD,而是保留了SIMD的特征。那么AMD是如何在保留SIMD特征的基础上采用MIMD架构的呢?

Tahiti拥有32组CU单元

为了解释这个问题,我们先抛开GCN架构的外围部分,从AMD宣称的CU单元,也就是“Compute Unit”计算单元开始了解。在AMD公布的架构图中,CU单元被表示成32组黑色的、命名为GCN的块。这32组CU单元占据了架构图的绝大部分面积。从单个CU单元来看,每个CU单元中有64个ALU(算术逻辑)单元,Radeon HD 7970标称的2048个流处理算术逻辑单元就是这样来的(32×64=2048个)。也就是说,这2048个ALU单元就是GCN架构的基础运算单元。

采用全新设计的CU单元

再进一步分析下去,每一个CU单元中,主要的是矢量计算单元,也就是Vector Unit。这个单元中有4个16路的SIMD计算子模块(每个SIMD模块拥有16个ALU,一共组成16路,可以处理同时并行的16个乘加指令计算),还配备了4个64KB的矢量寄存器(每个SIMD计算子模块各1个)。这4个16路的SIMD计算子模块是CU的数据执行基础。从单个CU的角度来看,1个CU在每个时钟周期内可以执行4个不同的16路矢量线程,可以称为MIMD(多指令多数据流)。而这4个矢量线程在执行时每个线程内都使用的是16路的SIMD计算子模块,因此GCN在底层上采用了单指令多数据流的设计方式。

这样一来,我们就不难理解AMD为什么称自己的产品设计为“基于SIMD阵列的MIMD架构”了。AMD依旧使用了SIMD阵列作为数据执行基础,但在更高一级的层面上采用了四路SIMD单元并行的设计方案。在实际数据操作中,AMD设计的线程调度器会每次派发64粒度的线程给CU单元,CU单元将其直接分配给由4个16路SIMD组成的计算单元计算,在理想的情况下一个CU单元一个周期就可以执行64粒度的线程操作。

相比上一代Cayman采用的VLIW 4架构,虽然它看起来都是每个周期可以执行四次操作,但实际上Cayman这四次操作是有一定的“关联度”的。因为这四次操作必须来自一条指令。如果来的指令只需要3个或者2个ALU计算,那么剩余的ALU只有闲置。但是在GCN这里,如果来的指令需要3个ALU计算,由于底层的四个16路的SIMD单元没有强制的捆绑关系,因此可以自由处理,理论效率接近100%。举个简单例子来说,如果有2个指令,分别同时需要2个ALU计算,在Cayman的单个VLIW 4单元执行时,这2个指令必须分两次执行。但是在GCN的CU上,可以一次执行来自两个指令的4个ALU操作,因此效率大大提升。我们举出这个孤立的例子,仅仅为了说明GCN的数据执行效率的变化,在实际处理中,AMD会采用各种手段来尽量优化分配指令,保证高效率——这并不是本文讨论的重点,我们只需要看到GCN在效率上相对前代产品的超高表现即可。总体而言,GCN与VLIW4(VLIW5)有一定关联,都采用并行运行方式,但两者在执行方式上却截然不同。采用VLIW设计的产品,使用的是提取指令级(ILP)的并行方式,GCN则采用线程级并行(TLP)方式,省略了指令打包、派送、解包的过程。

说完了重要的计算单元,CU中还有一些其它部分值得我们注意。比如除了矢量计算单元外,每个CU中还有一个用于执行整数、媒体指令和浮点原子操作的标量单元。这个标量单元拥有4KB的标量寄存器。此外,还有与数据分支指令有关的分支和信息单元、程序调度管理单元、纹理拾取模块、纹理滤波单元、共享的64KB只读本地数据缓存和16KB可读写L1数据缓存。这些部分在GCN架构的合理调配下,组成了精巧而灵活的CU单元。

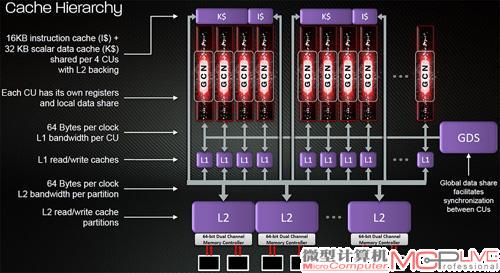

缓存:更灵活有效的缓存设计

在之前的Fermi上,我们看到了NVIDIA设计的极为优秀、层级鲜明、灵活可读取的缓存设计,这对通用计算来说帮助相当明显。不过当时AMD的Cayman采用比较保守的VLIW 4架构,缓存设计也基本没有太多亮点。这也是Cayman通用计算能力较差的原因之一。

在新的Tahiti上,AMD彻底改进了GPU的缓存方案,采用了类似Fermi的多级高速缓存搭配。在上一部分对CU的介绍中,我们看到了CU设计了缓存单元。实际上CU中的缓存仅仅是整个GCN架构缓存设计的一部分。除了每个CU中的标量单元和矢量单元都有自己的独立缓存外,每4个CU单元还可以共享16KB的矢量缓存以及32KB的指令缓存。另外每个CU还拥有16KB的L1可读写缓存,所有L1缓存都可以通过全局数据存储进行共享,这样32个CU一共拥有512KB的L1缓存。

除了L1缓存外,GCN还设计了可读写的L2缓存。L2缓存直接连接了显存控制器和L1缓存。每个显存控制器通道上连接的L2缓存都通过64bit位宽的总线和L1相连接,每个通道的L2缓存的容量为128KB。目前GCN架构的Radeon HD 7970拥有6个64bit的显存控制器,组成了384bit的显存带宽,因此L2缓存总量为768KB。

Tahiti使用了丰富的缓存设计

Tahiti如此设计L2缓存还带来了一个优势,那就是它的缓存可以与CPU内存数据同步,这样在通用计算中能大幅度提高GPU和CPU的数据交换能力。除此之外,Tahiti也能够支持X86虚拟内存功能。这个功能的主要作用是将GPU的显存映射为CPU的内存,CPU可以直接读取GPU显存中的数据,速度要比读取调用内存、硬盘中的数据速度快很多,能大幅度降低延迟。

Tahiti使用了丰富的缓存设计

纵观GCN的缓存设计,Tahiti形成了自己多层级的、可读写的缓存存取方案,不但大大改善了GCN架构的通用计算效能,也顺带提升了GCN架构在多种应用环境下的实际表现,让存储成为计算瓶颈的可能性大大降低。

曲面细分、ROP等功能:继续增强

在基本了解了AMD是如何设计GCN的核心部分、CU单元以及缓存设计后,我们从宏观角度来观察这颗芯片的其他方面的设计情况。

首先从架构顶端来看,GCN虽然和之前的Cayman比较类似,但加入了两个被称作ACE的引擎。ACE全称是Asynchronous Compute Engine,异步计算引擎。它的作用是调配管理所有的线程和任务队列,根据任务优先级优化和排序,并终将这些任务发配给CU单元进行计算。这大大增强了Tahiti对任务的优化排序能力,更有效地降低了计算中的无谓浪费和等待时间,同时也提升了缓存的使用效率。从数据处理的本质来看,图形计算依旧是顺序执行,GPU需要按照处理顺序一步一步地执行操作。ACE单元虽然不能像X86的CPU那样做到乱序执行,但至少能在目前有限的操作空间内大幅度提升GPU的效率。从互联角度来看,ACE联系了几乎所有的全局缓存、几何引擎以及指令处理单元。这也说明了其重要性。

AMD显卡的曲面细分能力一直为人所诟病,为此在AMD在Cayman上设计了双几何处理引擎,以加强曲面细分的性能。在Tahiti上,AMD继续沿用了这种设计,并宣称该双几何处理引擎从Cayman的第八代进化到第九代。根据AMD提供的官方数据来看,新的几何处理器引擎在加入了ACE的控制、提高了缓存设计以及强化了相关单元的情况下,相比Cayman至少可以达到1.8倍左右的性能提升(在5级的曲面细分下),多可以达到4倍的提升(在14级曲面细分系数下)。在更高的曲面细分系数如20级以后,至少也有3.5倍的性能提升。

接下来是Tahiti的ROP和显存控制器设计。以Radeon HD 7970为例,这款显卡拥有32个ROP单元,每周期可以执行32个色彩处理以及128个Z/Stencil处理。从参数来看,虽然ROP数量相比上代Cayman的产品没有提升,但和ROP性能有关联的显存带宽得到了提升—这是AMD近年来首次采用384bit显存位宽,相比上代256bit提升了约50%。再加上AMD一贯的高频率显存,采用GCN架构的Radeon HD 7970的显存带宽高达264GB/s。更高的显存带宽,在对显存带宽渴求度比较高的应用如抗锯齿、高分辨率等计算中,会有比较明显的性能提升。

用户评论

-

这篇文章写的不错,美中不足是没有对照GPU和CPU在通用计算和浮点运算的差异与数据.如果有此数据就可知道在APU明年实现真正的CPU/GPU统一寻址后,而APU不仅仅是CPU、GPU的简单物理整合,更是深层次的融合,而实现这种融合的关键之一就是CPU、GPU的统一内存空间寻址。经过Llano、Trinity的两代铺垫之后,明年的Kaveri将终完全实现这一梦想。彻底实现统一寻址后,CPU、GPU之间就可以有通用的用户调用,并共享数据,从而避免相互的数据拷贝和带宽浪费,也摆脱对高内存频率的依赖,为二者的更进一步融合奠定坚实的基础。无论是3D图形性能还是并行计算性能,都会因此上一个台阶。这才是HD7970架构的先进之处.但是总的来说很好.