45nm远不是极限!神秘的处理器制程工艺

摩尔定律指导集成电路(IC,Integrated Circuit)工业飞速发展到今天已经40多年了。在进入21世纪的第8个年头,各类45nm芯片开始批量问世,标志着集成电路工业终于迈入了低于50nm的纳米级阶段。而为了使45nm工艺按时“顺产”,保证摩尔定律继续发挥作用,半导体工程师们做了无数艰辛的研究和改进—这也催生了很多全新的工艺特点,像大家耳熟能详的High-K、沉浸式光刻等等。按照业界的看法,45nm工艺的特点及其工艺完全不同于以往的90nm、65nm,反而很多应用在45nm制程工艺上的新技术,在今后可能贯穿到32nm甚至22nm阶段。今天就让我们通过一个个案例,来探索一下将伴随我们未来5年的技术吧。

你能准确说出45nm是什么宽度吗?

得益于厂商与媒体的积极宣传,就算非科班出身,不是电脑爱好者的大叔们也能知道45nm比

65nm更加先进。但如果要细问45nm是什么的长度,估计很多人都难以给出一个准确的答案。

而要理解这个问题,就要从超大规模集成电路中基本的单元—MOS(Metal Oxide

Semiconductor金属氧化物半导体)晶体管说起。

我们用半导体制作MOS管就是利用其特殊的导电能力来传递0或者1的数字信号。在栅极不通电的情况下,源区的信号很难穿过不导电的衬底到达漏区,即表示电路关闭(数字信号0);如果在栅极和衬底间加上电压,那么衬底中的电荷就会在异性相吸的作用下在绝缘氧化层下大量聚集,形成一条细窄的导电区,使得源区和漏区导通,那么电流就可以顺利从源区传递到漏区了(信号1)。这便是MOS基本的工作原理。

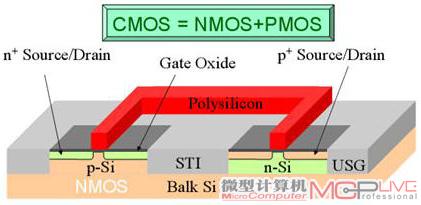

在一块高纯硅晶圆上(在工艺中称为“P型半导体衬底”)通过离子扩散的方法制作出两个N型半导体的阱——通俗地讲P型是指带正电的粒子较多,N型则是带负电的粒子比较多。再通过沉积、光刻、氧化、抛光等工艺制造成如图中所示的MOS管,两个阱的上方分别对应源区(source)和漏区(

drain),中间的栅区(gate)和下方的衬底中间用一层氧化绝缘层隔开。我们通常说的90nm或者45nm工艺,就是指的栅极下方两个阱之间的长度,称之为导电沟道长度。

上图中给我们勾勒出来的是一个NMOS,当栅极接正向电压时,NMOS会导通。事实上还存在另外一种PMOS,其性质完全相反,当栅极接负电时,通过在绝缘区下方聚集正电荷来导通。

在实践中,工程人员很快就发现了单个MOS管在作为逻辑电路导通时,会有源源不断的电流通过,这使得MOS管功率居高不下。而事实上我们只需要传递信号就行了,无论是用电流,又或者是用电压方式,而不需要MOS管有较高的功耗。为了降低MOS管的工作功耗,可科学家们又开发了

CMOS(Complementary Metal-Oxide Semiconductor 互补金属氧化物半导)电路。

CMOS的电路结构

物如其名,CMOS中包含NMOS和PMOS各一个,并且串联在一起。由于PMOS和NMOS的导通特性正好相反,因此无论什么时候都只有一个MOS管导通,另一个必然关闭。这样就起到了传递电压信号,但是无电流功的产生。

理论上CMOS的静态功耗应该为0,但是受材料和制造工艺的限制,CMOS的实际功耗却是不能忽略不计的,这样也就有了后面的各种改良工艺。